# **DALPU-4**

## **NEOWINE Crypto and Authentication**

## DATASHEET

#### Features

#### 32-bit ARM Cortex-M3 Core

- Nested Vectored Interrupt Controller(NVIC): 1 Wake up and 1 peripheral interrupt

- 16-bit or 32-bit System timer (Sys Tick): System timer for OS task management

- Creation and Management of Cipher Key

#### **On-chip Memory**

- EEPROM

- 128 KB

- Configuration/Key/User data storage

- 15 User Zones of 2 Kbits Each

- Retention 10 years

- Erase/Write Endurance: 100K

- SRAM

- On chip 32 Kbytes

#### Serial Interface

- UART

- Full duplex double buffer

- Parity can be enabled or disabled

- Built-in dedicated baud rate generator

- Various error detection functions (parity error, framing errors, and overrun errors)

- External x-tal for UART

- SPI0, SPI2

- Slave, Mode 0

- Up to 40 MHz SCK

- Symmetric cipher core control

- SPI1

- Master/Slave

- Master: Up to 10 MHz SCK

- Slave: Up to 1.5 MHz SCK

- Mode 0, 1, 2, 3

- GPIO

- 4 GPIOs

#### Clock, Reset and Voltage

- Clock

- Built in OSC.

- Main Clock: 50 fMHz

- Reset

- Built in power on reset

- Software reset

- 1.5V, 3.3V Supply Voltage

#### Debug

Serial Wire Debug Port(SW-DP)

#### Low Power Consumption Mode

- The GPIO is sufficient to power up and down

- PMU clock gating of Cortex-M3

#### Asymmetric cipher function

- ECC-P256, RSA-4096

- ECDSA, ECDH

#### Symmetric cipher function

- AES-128/256, ARIA-128/256

- Modes of Operation: Confidentiality (ECB, CBC, CFB, OFB, CTR)

- Creation and Management of Cipher Key

#### **Crypto Device function**

- User ID, User Serial (Manufacture ID), MIDR, RVC

- PUF

- Generate random using two different phase counters

#### Application

- Print cartridge, GPS, Navigation

- Mobile Device, IPC, CCTV, DVD

- Set-Top Boxes (STBs), Etc.

#### Standards

- ECC, RSA FIPS 186-3, 186-4

- AES-128/256 FIPS 140-2

- TRNG NIST SP 800-90B compatibility

#### **Benefits**

- Read/Write, Encrypted, or Read-only User Zone Options

- Ease use of Crypto Device to replace of existing EEPROM devices

- Authenticate Consumer products, Components, and Network equipment

- Protect Sensitive Firmware

- Securely Store Sensitive Data

- Manage Warranty Claims

- Securely Store Identity Data

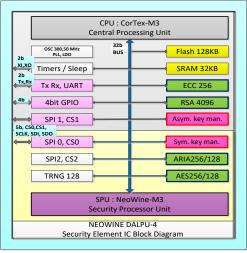

Block Diagram

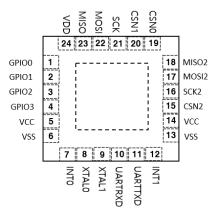

#### Package

QFN 4x4-25L (4mm X 4mm X 0.75mm)

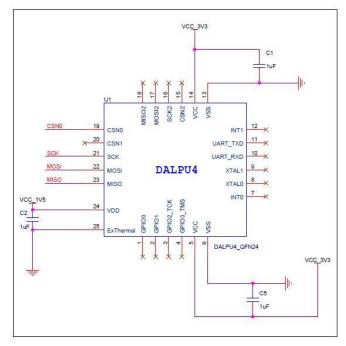

#### **Schematic Diagram**

Application Circuit

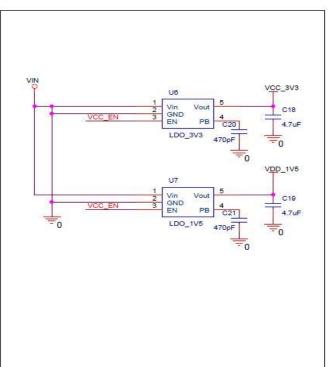

DALPU-4 Power Circuit

## Contents

| Con  | tents                                  | 3  |

|------|----------------------------------------|----|

| Figu | ire                                    | 4  |

| 1    | Introduction                           | 5  |

|      | 1.1 Applications                       | 5  |

|      | 1.2 Device Features                    | 5  |

|      | 1.3 Crypto Operation                   | 5  |

| 2    | Device configurations                  | 6  |

|      | 2.1 Symmetric Cipher Parts             | 6  |

|      | 2.2 Asymmetric Cipher Parts            | 8  |

| 3    | Device Functions                       | 10 |

| 4    | E-MCU to DALPU-4 Interface             | 11 |

|      | 4.1 SPI0 Interface                     | 11 |

|      | 4.2 SPI1 Interface                     | 12 |

| 5    | Address Map                            | 13 |

|      | 5.1 CORTEX-M3 AMBA Bus Address Map     | 13 |

|      | 5.2 Symmetric Cipher parts Address Map | 14 |

| 6    | Registers                              | 16 |

|      | 6.1 SPI0 registers                     | 16 |

|      | 6.2 CORTEX-M3 registers                | 41 |

| 7    | EEPROM Configuration                   | 46 |

| 8    | Revision History                       | 47 |

## Figure

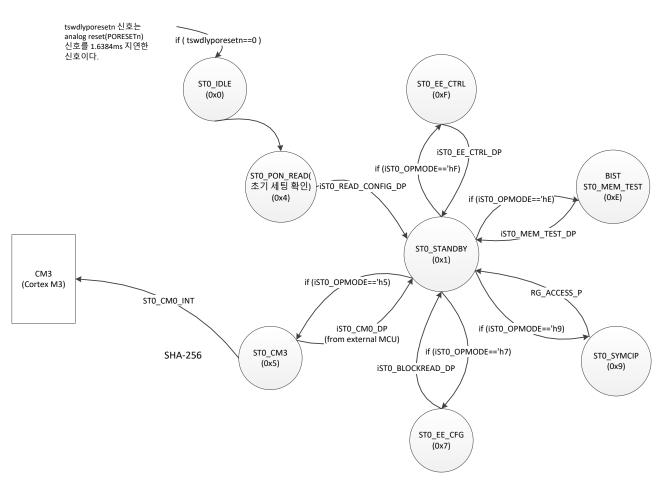

| Figure 2-1 Main Control state machine diagram             | . 7 |

|-----------------------------------------------------------|-----|

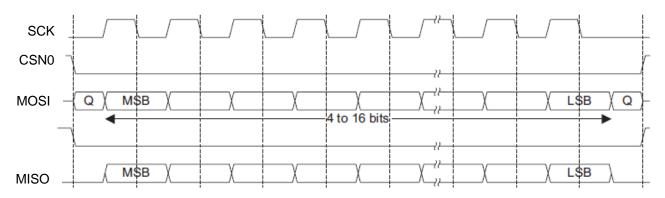

| Figure 4-1 SPI0 Normal Mode Write in Address Mode         | 11  |

| Figure 4-2 SPI0 Normal Mode Read in Address Mode          | 11  |

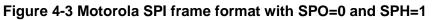

| Figure 4-3 Motorola SPI frame format with SPO=0 and SPH=1 | 12  |

## 1 Introduction

The following sections introduce the features and functions of the DALPU-4 crypto device.

## 1.1 Applications

DALPU-4 is designed to apply high security rules to the product. These security rules can be used to protect the data, to protect the functionality of the product, and to prevent replication.

• Product authentication

DALPU-4 has the function of preventing reproduction or illegal modification of products.

• Exchanging Security Keys

DALPU-4 has Public-Key Cryptosystems. User can use this function to exchange keys safely.

• Storing Security Data

You can store secret keys used for ciphering. Can save configuration, calibration or other secret data.

## 1.2 Device Features

The DALPU-4 has an Electrically Erasable Programmable Read-Only Memory (EEPROM). The EEPROM can be used for key storage, miscellaneous write/read data, read-only, secret data, consumption logging, and security configuration. DALPU-4 has 32-bit ARM Cortex-M3 Core. This core is in charge of public key operation. DALPU-4 has 32 Kbytes SRAM, it is used for M3 code execution region and user code region. DALPU-4 has SPI0, SPI1, UART and GPIO interfaces. SPI0 can have a slave mode. With SPI0 user can control symmetric cipher core. SPI1 can have both a slave and a master mode. With SPI1 in a slave mode, user can control asymmetric cipher core. DALPU-4 has a power saving mode. In sleep mode internal oscillator is disabled. DALPU-4 has a symmetric cipher function which is ECC-P256, ECDSA and ECDH. DALPU-4 has a symmetric cipher function which is AES-128/256. AES supports ECB, CBC, CFB, OFB, CTR operating modes..

## 1.3 Crypto Operation

DALPU-4 save control information to the EEPROM. These control information is a configuration data. The configuration data is protected by password. DALPU-4 can encrypt or decrypt an input data with AES. And the result is read by an external MCU. DALPU-4 encrypt user data and save to a EEPROM. External MCU(E-MCU) can read saved data. When E-MCU request the saved data, the DALPU-4 returns encrypted data. DALPU-4 has authentication function using SHA.

## 2 Device configurations

DALPU-4 is composed of two parts. One is asymmetric cipher part and the other is symmetric cipher part. The asymmetric cipher part is composed of a CORTEX-M3 and an asymmetric cipher hardware. The symmetric cipher part is a Security Processor Unit(SPU). The symmetric cipher part is composed of a symmetric cipher hardware and a main control hardware. The asymmetric cipher part take charge of ECC-P256, RSA-2048, ECDSA and ECDH. The symmetric part take charge of AES-128/256, SHA-256 and main control function. The main control function consists of state machine hardware. The following sections explain operation of each functions. An external MCU controls DALPU-4. The DALPU-4 has two interfaces to the external MCU. One is SPI0 for the symmetric cipher part. The other is SPI1 for the asymmetric cipher part. The external MCU can control DALPU-4 main control hardware through SPI0 interface. The external MCU can control a CORTEX-M3 and asymmetric cipher hardware through SPI1.

## 2.1 Symmetric Cipher Parts

The Symmetric Cipher part consist of a Symmetric Cipher Hardware and a Main Control Hardware. First the Main Control Hardware parts are as follows.

### 2.1.1 MAIN CONTROL HARDWARE

The Main Control Hardware can have 14 main states. Each main state has independent operation. Most of operations are processed in one main state, but some operations are processed in several main states. When the DALPU-4 wakes up, it processes the initial procedures automatically, then goes to ST0\_STANDBY state. Usually, if DALPU-4 finishes a certain function, it always goes to ST0\_STANDBY state. A hardware logic sends main state to ST0\_STANDBY state when the DALPU-4 finishes a function, or E-MCU must control to send main state to ST0\_STANDBY state in some functions. If DALPU-4 finishes state abnormally, it may can't process another function normally.

Figure 2-1 Main Control state machine diagram

Figure 2-1 shows every state which the main state can have. When power is on, the DALPU-4 begins an initial procedure. The initial procedure starts from ST0\_IDLE state, and stops to ST0\_STANDBY state. The initial procedure starts automatically when the power is up. User can skip ST0\_CHK\_RSFLAG state. See the following sections to control skip function of ST0\_CHK\_RSFLAG state.

### 2.1.1.1 ST0\_PON\_READ STATE CONTROL

The hardware prepares initial values to process a normal operation. The DALPU-4 main control hardware executes this state automatically

#### 2.1.1.2 ST0\_CM3 STATE CONTROL

The hardware cannot set this state, the E-MCU can set this state through SPI0. The E-MCU controls RG\_ST0\_OPMODE(0x1\_0604) register to set ST0\_CM0 state. If the E-MCU want to communicate with CORTEX-M0, E-MCU sets ST0\_CM0 state first. After then, E-MCU sends control information to CORTEX-M0. If CORTEX-M0 receive control information, it controls asymmetric cipher hardware. Some of CORTEX-M0 control may affect the symcipher hardware blocks. A detail explanation is given later of this document.

### 2.1.1.3 ST0\_SYMCIP STATE CONTROL

The hardware cannot set this state, the E-MCU can set this state through SPI0. The E-MCU controls RG\_ST0\_OPMODE(0x1\_0604) register to set ST0\_SYMCIP state. DALPU-4 operates symmetric cipher functions in this state.

Second the Symmetric Cipher Hardware configurations are as follows.

#### 2.1.2 SYMMETRIC CIPHER HARDWARE

Symmetric cipher hardware handles the encryption and decryption using AES and the authentication using SHA. It also generates random. It manages writing and reading of EEPROM. It manages a key generation, key storage and key change.

## 2.2 Asymmetric Cipher Parts

Asymmetric cipher parts consist of the CORTEX-M3 and the Asymmetric Cipher Hardware. The CORTEX-M3 controls the asymmetric Cipher Hardware. The Asymmetric Cipher Hardware is responsible for performing ECC, ECDH and ECDSA algorithms.

### 2.2.1 CORTEX-M3 HARDWARE

#### 2.2.1.1 CORTEX-M3 CORE

The Cortex-M3 processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- simple, easy-to-use programmers model

- highly efficient ultra-low power operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with the rest of the Cortex-M processor family.

#### 2.2.1.2 CORTEX-M3 CORE PERIPHERALS

The Cortex-M3 core peripherals are:

#### NVIC

An embedded interrupt controller that supports low latency interrupt processing.

#### System Control Block

The System Control Block (SCB) is the programmers model interface to the processor. It provides system implementation information and system control, including configuration, control, and reporting of system exceptions.

#### **Optional system timer**

The optional system timer, SysTick, is a 24-bit count-down timer. If implemented, use this as a Real Time Operating System (RTOS) tick timer or as a simple counter.

#### Public Key Engine (Asymmetric Cipher)

The PK Crypto Engine is a very flexible solution based on a scalable array of dual-field processing elements that can be used to execute all operations & algorithms required for PK Crypto-systems:

- Elliptic Curve Cryptography (ECC)

- •Diffie-Hellman (D-H & ECD-H) Key Exchange

- Digital Signature Algorithm (DSA) and Elliptic Curve Digital Signature Algorithm (ECDSA)

- Primality Test (Rabin-Miller) & Key Generation

- Any other crypto algorithm can be supported on request

#### Embedded EEPROM and SRAM

DALPU-4 has 128 KB of EEPROM and SRAM. The EEPROM stores the cortex-M3 code and the rom code of the asymmetric cipher. The SRAM is shared by the Cortex-M3 and Asymmetric Cipher, Symmetric Cipher for TLS.

#### **Registercm3**

Registercm3 is basically used by Cortex M3 to control the EEPROM. Generates the control signals needed to write to or read from the EEPROM. It is also used when selecting IO or SPI, and also used when Cortex M3 generates a random value.

#### Timers

The Dual Input Timers module, Timers is an AMBA slave module and connects to the APB. The Dual-Timer module consists of two programmable 32/16-bit down counters that can generate interrupts on reaching zero. A Timer module can be programmed for a 32-bit or 16-bit counter size and one of three timer modes using the Control Register. The operation of each Timer module is identical. It has one of three timer modes:

- free-running

- periodic

- one-shot

#### UART

The UART is an AMBA slave module that connects to the Advanced Peripheral Bus (APB). The UART provides:

• Compliance to the AMBA Specification (Rev 2.0) onwards for easy integration into SoC implementation.

• Separate 16x8 transmit and 16x12 receive First-In, First-Out memory buffers(FIFOs) to reduce CPU interrupts.

• Programmable FIFO disabling for 1-byte depth.

• Programmable baud rate generator. This enables division of the reference clock by (1x16) to (65535 x16) and generates an internal x16 clock. The divisor can be a fractional number enabling you to use any clock with a frequency >3.6864MHz as the reference clock.

• Standard asynchronous communication bits (start, stop and parity). These are added prior to transmission and removed on reception.

#### **GPIOs (General-Purpose Input/Output)**

The GPIO is a general purpose I/O device. It has the following properties:

- three registers : Data, Direction, Interrupt Registers

- 32 input or output lines with programmable direction

- word and halfword read and write access

- address-masked byte write to facilitate quick bit set and clear operations

- address-masked byte read to facilitate quick bit test operations

- maskable interrupt generation based on input value change.

#### SPI

It has SPI0, SPI1 and SPI2, SPI0 and SPI2 only operates as slave, and it is used by EMCU to control Symmetric Cipher. SPI1 is used by Cortex-M3 to control Symmetric Cipher. It can operate as master or slave.

#### 2.2.2 ASYMMETRIC CIPHER HARDWARE

This Public Key Engine(Asymmetric Cipher) has following features.

- •1 multiplier architecture

- ECC/ECDH/ECDSA operations up to 512 bits

- ECDSA p256

- Supports prime field GF(p) and binary field GF(2<sup>m</sup>) fields .

## 3 Device Functions

## 3.1.1 AES ENCRYPTION (DECRYPTION) FUNCTION

AESEncrypt control takes the plaintext from 16 bytes and encryptions and outputs ciphertext. The key used for AES encryption are notified to DALPU-4 by E-MCU using the RG\_EE\_KEY\_AES\_xN register. AESDecrypt control takes the ciphertext input from 16 bytes and decodes and outputs a plaintext. The keys used for AES decryption are notified to DALPU-4 by E-MCU using the RG\_EE\_KEY\_AES\_xN register.

## 3.1.2 **AES ENCRYPTION WRITE(READ) FUNCTION**

With AESEncwrite control, 16 bytes of data can be written to the EE\_USER\_ZONE\_Mx area of the EEPROM. AESEncwrite procedures are as follows. E-MCU encrypts the 16 bytes plaintext into ciphertext using the EE\_KEY\_AES\_xN key and writes it to DALPU-4. For DALPU-4, receive the 16 bytes data and decrypt it using the EE\_KEY\_AES\_xN key and store it in the appropriate EEPROM. The AESEncREad procedure is as follows. E-MCU sends control that DALPU-4 reads user data 16 bytes from EEPROM. For DALPU-4, read the 16 bytes plain text from EEPROM and cipher it using EE\_KEY\_AES\_xN key. E-MCU reads the cipher text after waiting DALPU-4 finish decryption. AES Encryption Write (or Read) function encrypt or decrypt 16 bytes at one time. E-MCU can process 4 encryptions (or decryptions) continuously. But E-MCU should not control EEPROM address cross over the page boundary of EEPROM.

### 3.1.3 EEPROM ERASE FUNCTION

This function enables you to read or clear EEPROM specific information. User use this function for special purpose. Users should review sufficiently before using this feature to determine its intended use. This function is usually not used.

## 3.1.4 **PUF (PHYSICAL UNCRONABLE FUNCTION)**

This chapter describes how to create and use the Root Serial corresponding to the unique number of DALPU-4. The Root Serial is a unique number for each device. And this value is a fixed value and cannot be changed. When

### 3.1.5 **RANDOM GENERATION FUNCTION**

Random Generator can generate random values in three ways. The first is to generate a random value through SPI0 when the user wants a random value. The second one can be created when a random value is desired in Cortex-M0. Finally, Symmetric cipher can generate and take random values when they are needed.

## 3.1.6 ECDH (ELLIPTIC CURVE DIFFIE HELLMAN) FUNCTION

Elliptic Curve Diffie-Hellman key exchange is one way to generate key values on an elliptic curve and exchange encryption keys so that they can share a shared key with other keys on an unencrypted network. DALPU-3 supports ECC P-256, P384, P-521 curves etc and supports up to 512 bits.

## 3.1.7 ECDSA(ELLIPTIC CURVE DIGITAL SIGNATURE ALGORITHM) FUNCTION

ECDSA implements electronic signatures on elliptic curves and works on ECC P-256, P-384, and P-521 curves etc. ECDSA operations can be executed in both fields GF(p)-prime field or GF(2<sup>m</sup>)-binary field. ECDSA signatures can be generated and verified.

## 4 E-MCU to DALPU-4 Interface

DALPU-4 has SPI0, SPI1, SPI2, UART and GPIO interfaces. In generally DALPU-4 is used as a security function chip not as a MCU. When the DALPU-4 is used as a security function chip, SPI0 and SPI2 is slave mode. When the DALPU-4 is used as a MCU, SPI1 is master mode.

## 4.1 SPI0, SPI2 Interface

SPI0, SPI2 has write / read protocol as shown in Figure 4-1 and 4-2 below. SPI0, SPI2 is primarily used by external MCUs to control symmetric cipher.

## 4.1.1 SPI0 PROTOCOL TIMING DIAGRAM

#### 4.1.1.1 SPIO NORMAL MODE WRITE

#### Figure 4-1 SPI0 Normal Mode Write in Address Mode

|      | SPI Address Mode : Write |                                              |   |

|------|--------------------------|----------------------------------------------|---|

| CSN0 |                          |                                              |   |

| SCK  |                          |                                              | _ |

| MOSI |                          | <br>DataN-3<br>76154432110763432110763432100 | _ |

| MISO | High Impedence           |                                              | _ |

#### 4.1.1.2 SPI0 NORMAL MODE READ

#### Figure 4-2 SPI0 Normal Mode Read in Address Mode

|      | SPI Address Mode : Read |                                                         |                                                |  |

|------|-------------------------|---------------------------------------------------------|------------------------------------------------|--|

| CSN0 | 7                       |                                                         |                                                |  |

| SCK  |                         |                                                         |                                                |  |

| MOSI | Addro dummy 8 o         | de                                                      |                                                |  |

| MISO | High Impedence          | Data0<br>7X6(3X4)3(21)0(7)6(5)4(3)2(1)0(7)6(3(4)3(21)0) | <br>Data N-3<br>765243221007265432110765432110 |  |

## 4.2 SPI1 Interface

SPI1 is used by EMCU to control PKE(Asymmetric Cipher) through Cortex-M3. It basically supports Motorola SPI frame type. The main feature of the Motorola SPI format is that the inactive state and phase of the SCK signal are programmable through the SPO and SPH bits within the SPI1 control register.

#### SPO, clock polarity

When the SPO clock polarity control bit is LOW, it produces a steady state low value on the SCK pin. If the SPO clock polarity control bit is HIGH, a steady state high value is placed on the SCK pin when data is not being transferred.

#### SPH, clock phase

The SPH control bit selects the clock edge that captures data and allows it to change state. It has the most impact on the first bit transmitted by either allowing or not allowing a clock transition before the first data capture edge. When the SPH phase control bit is LOW, data is captured on the first clock edge transition. If the SPH clock phase control bit is HIGH, data is captured on the second clock edge transition.

For Frame format used between EMCU and Cortex-M3, set SPO to 0 and SPH to 1. The transfer signal sequence for Motorola SPI format with SPO=0, SPH=1 is shown in Figure 4-3, which covers both single and continuous transfers.

## 5 Address Map

DALPU-4 has CORTEX-M3. The CORTEX-M3 has AMBA bus. And DALPU-4 has address map for the Symmetric Cipher parts and the Asymmetric Cipher parts. CORTEX-M3 AMBA Bus Address Map

## Table 5-1 CORTEX-M3 AMBA Bus Address Map

|             |                             |            | 0x4001_0000 |

|-------------|-----------------------------|------------|-------------|

|             |                             | Asymcipher | 0x4000_9000 |

|             |                             | WatchDog   | 0x4000_8000 |

|             |                             | UART0      | 0x4000_7000 |

| 0xFFFF_FFF  |                             | Reserved   | 0x4000_6000 |

| 0x4002_0000 | Reserved                    | Reserved   | 0x4000_5000 |

| 0x4001_F000 | System Controller Registers | Reserved   | 0x4000_4000 |

| 0x4001_2000 | Reserved                    | SSP        | 0x4000_3000 |

| 0x4001_1000 | Reserved                    | Dual Timer | 0x4000_2000 |

| 0x4001_0000 | AHB GPIO0                   | Tlmer1     | 0x4000_1000 |

| 0x4000_0000 | APB subsystem peripherals   | Timer0     | 0x4000_0000 |

| 0x2001_0000 | Reserved                    |            |             |

| 0x2000_0000 | SRAM 32KByte                |            |             |

| 0x0101_0000 | Reserved                    |            |             |

| 0x0100_0000 | bootloader memory           |            |             |

| 0x0003_0000 | Reserved                    |            |             |

| 0x0002_0000 | Registercm3                 |            |             |

| 0x0000_0000 | EEPROM 128KByte             |            |             |

## 5.1 Symmetric Cipher parts Address Map

Symmetric Cipher parts include EEPROM and the symmetric cipher core. E-MCU can access EEPROM and registers with SPI0 interface.

| ADDR(HEX)            | M0     | CIP<br>CORE | Туре     |                      | NAME/RANGE        |                                        | BYTE<br>SIZE(DEC)              | DESCRIPTION                                                                                              |                                                                                                                                                                               |

|----------------------|--------|-------------|----------|----------------------|-------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . ,                  | ACCESS | ACCESS      |          | Group1               | Group2            | Group3                                 |                                |                                                                                                          |                                                                                                                                                                               |

| 0x0E800<br><br>E8FF  |        |             |          | EE_CM0/<br>EE_SYMCIP | EE_KEY_ASYMCIP_xN | EE_KEY_ASYMCIP_x0<br>EE_KEY_ASYMCIP_x3 | 256                            | 1. KEY zone<br>2. Asymmetric Key storage<br>area (64Byte * 4)                                            |                                                                                                                                                                               |

| E900<br><br>E9FF     |        |             | EEPROM   | EEPROM               |                   | EE_KEY_AES_xN                          | EE_KEY_AES_x0<br>EE_KEY_AES_x3 | 256                                                                                                      | 1. KEY zone<br>2. Symmetric Key storage<br>area (64Byte * 4)                                                                                                                  |

| EA00<br><br>EAFF     |        |             |          |                      |                   | EE_RS_xN                               | EE_RS_x0                       | 256                                                                                                      | 1. KEY zone<br>2. ROOT SERIAL storage<br>area (64Byte * 4)                                                                                                                    |

| EB00<br><br>F0FF     |        |             |          |                      | EE_SYMCI          | EE_CONFIG                              | EE_CONFIG_NW 등                 | 1536                                                                                                     | <ol> <li>Configuration zone</li> <li>This zone contains all<br/>information to control the<br/>CM0 zone, KEY zone,</li> <li>Configuration zone, and<br/>User zone.</li> </ol> |

| F100<br><br>0x0FFFF  |        |             |          |                      |                   |                                        |                                | EE_USER_ZONE_M                                                                                           | EE_USER_ZONE_M01<br>EE_USER_ZONE_M15                                                                                                                                          |

| 0x10000<br><br>1003F |        |             |          | IUM                  |                   |                                        | 64                             | IUM(RESERVED)                                                                                            |                                                                                                                                                                               |

|                      |        |             |          | RESERVED             |                   |                                        |                                |                                                                                                          |                                                                                                                                                                               |

| 0x10100<br><br>1013F |        |             | REGISTER | RG_EEBUF             |                   |                                        | 64                             | Used for EEPROM write<br>operations and BIST test<br>application. Not used for<br>EEPROM read operation. |                                                                                                                                                                               |

| 0x10140              |        |             | NEGISTER | RESERVED             |                   |                                        |                                |                                                                                                          |                                                                                                                                                                               |

|                      |        |             |          | RESERVED             |                   |                                        |                                |                                                                                                          |                                                                                                                                                                               |

| 0x10200<br>          |        |             |          | RESERVED             |                   |                                        |                                |                                                                                                          |                                                                                                                                                                               |

## Table 5-2 EEPROM and register Address Map(SPI0)

| ADDR(HEX) | MO     | CIP<br>CORE | Туре |           | NAME/RANGE   |               | BYTE<br>SIZE(DEC) | DESCRIPTION                |

|-----------|--------|-------------|------|-----------|--------------|---------------|-------------------|----------------------------|

|           | ACCESS | ACCESS      |      | Group1    | Group2       | Group3        |                   |                            |

| 1023F     |        |             |      |           |              |               |                   |                            |

|           |        |             |      | RESERVED  |              |               |                   |                            |

| 0x10300   |        |             |      |           |              |               |                   | First ENC input 128 bits   |

|           |        |             |      |           |              | RG_ENCINBUF0  | 16                | buffer share with          |

| 1030F     |        |             |      |           |              |               |                   | RG_CMDBUF[15:0].           |

| 0x10310   |        |             |      |           | RG_ENCINBUF  |               |                   | Second ENC input 128 bits  |

|           |        |             |      |           |              | RG_ENCINBUF1  | 16                | buffer share with          |

| 1031F     |        |             |      |           |              |               |                   | RG_CMDBUF[31:16].          |

| 0x10320   |        |             |      |           |              |               |                   | First ENC output 128 bits  |

|           |        |             |      |           |              | RG_ENCOUTBUF0 | 16                | buffer share with          |

| 1032F     |        |             |      |           |              |               |                   | RG_CMDBUF[47:32].          |

| 0x10330   |        |             |      |           | RG_ENCOUTBUF |               |                   | Second ENC output 128      |

|           |        |             |      |           |              | RG_ENCOUTBUF1 | 16                | bits buffer share with     |

| 1033F     |        |             |      |           |              |               |                   | RG_CMDBUF[63:48].          |

| 0x10400   |        |             |      | RG_EEBUF  |              |               |                   | First DEC input 128 bits   |

|           |        |             |      |           |              | RG_DECINBUF0  | 16                | buffer share with          |

| 1040F     |        |             |      |           |              |               |                   | RG_CMDBUF[15:0].           |

| 0x10410   |        |             |      |           | RG_DECINBUF  |               |                   | Second DEC input 128 bits  |

|           |        |             |      |           |              | RG_DECINBUF1  | 16                | buffer share with          |

| 1041F     |        |             |      |           |              |               |                   | RG_CMDBUF[31:16].          |

| 0x10420   |        |             |      |           |              |               |                   | First DEC output 128 bits  |

|           |        |             |      |           |              | RG_DECOUTBUF0 | 16                | buffer share with          |

| 1042F     |        |             |      |           |              |               |                   | RG_CMDBUF[47:32].          |

| 0x10430   |        |             |      |           | RG_DECOUTBUF |               |                   | Second DEC output 128 bits |

|           |        |             |      |           |              | RG_DECOUTBUF1 | 16                | buffer share with          |

| 1043F     |        |             |      |           |              |               |                   | RG_CMDBUF[63:48].          |

|           |        |             |      | RESERVED  |              |               | 1                 |                            |

| 10500     |        |             |      |           |              |               |                   |                            |

|           |        |             |      | RESERVED  |              |               | 32                | RESERVED                   |

| 1051F     |        |             |      |           |              |               |                   |                            |

|           |        |             |      | RESERVED  |              |               |                   |                            |

| 0x10600   |        |             |      |           |              |               | 1                 |                            |

|           |        |             |      | RG_SYMCIP |              |               | 512               | DALPU-3                    |

| 107FF     |        |             |      |           |              |               |                   | control registers.         |

## 6 Registers

## 6.1 SPI0 registers

### 6.1.1 **RG\_EEBUF BUFFER ADDRESS MAP**

RG\_EEBUF is used for encryption, decryption and EEPROM write.

SPI0 address width is 17 digits.

| ADDR(HEX)      | WR      | BIT       | NAME/RANGE                              | DESCRIPTION                                   | RESET |

|----------------|---------|-----------|-----------------------------------------|-----------------------------------------------|-------|

|                |         |           |                                         |                                               | VALUE |

| RG_EEBUF100    | )       |           |                                         |                                               |       |

| Use this regis | ster to | write a   | and read the data in DALP               | U-3 internal RG_EEBUF buffer. And it is       |       |

| used to write  | data    | to EEPI   | ROM.                                    |                                               |       |

| The RG_EEBU    | IF buf  | fer size  | is 512 bits(64 Bytes).                  | 1                                             | _     |

| 0x10100        | WR      | [7:0]     | MCU : RG_EEBUF[0]                       | RG_EEBUF[0]                                   | 0x00  |

|                | WR      | [7:0]     |                                         |                                               | 0x00  |

| 1010F          | WR      | [7:0]     | MCU : RG_EEBUF[15]                      | RG_EEBUF[15]                                  | 0x00  |

| 0x10110        | WR      | [7:0]     | MCU : RG_EEBUF[16]                      | RG_EEBUF[16]                                  | 0x00  |

|                | WR      | [7:0]     |                                         |                                               | 0x00  |

| 1011F          | WR      | [7:0]     | MCU : RG_EEBUF[31]                      | RG_EEBUF[31]                                  | 0x00  |

| 0x10120        | WR      | [7:0]     | MCU : RG_EEBUF[32]                      | RG_EEBUF[32]                                  | 0x00  |

|                | WR      | [7:0]     |                                         |                                               | 0x00  |

| 1012F          | WR      | [7:0]     | MCU : RG_EEBUF[47]                      | RG_EEBUF[47]                                  | 0x00  |

| 0x10130        | WR      | [7:0]     | MCU : RG_EEBUF[48]                      | RG_EEBUF[48]                                  | 0x00  |

|                | WR      | [7:0]     |                                         |                                               | 0x00  |

| 1013F          | WR      | [7:0]     | MCU : RG_EEBUF[63]                      | RG_EEBUF[63]                                  | 0x00  |

| 10140          |         |           | RESERVED                                |                                               |       |

| 102FF          |         |           | RESERVED                                |                                               |       |

| RG EEBUF300    | )       |           |                                         |                                               |       |

| _              |         | is the ir | nput and output buffer wh               | en performing AES encryption.                 |       |

| 0x10300        | WR      | [7:0]     | RG_EEBUF[0]<br>MCU :<br>RG_ENCINBUF0[0] | Encoder0 input buffer or Key0 input<br>buffer | 0x00  |

| ADDR(HEX)                     | WR | BIT      | NAME/RANGE                                 | DESCRIPTION                                   | RESET<br>VALUE |

|-------------------------------|----|----------|--------------------------------------------|-----------------------------------------------|----------------|

|                               |    | [7:0]    |                                            | Encoder0 input buffer or Key0 input<br>buffer | 0x00           |

| 1030F                         |    | [7:0]    | RG_EEBUF[15]<br>MCU :<br>RG_ENCINBUF0[15]  | Encoder0 input buffer or Key0 input<br>buffer | 0x00           |

| 0x10310                       |    | [7:0]    | RG_EEBUF[16]<br>MCU :<br>RG_ENCINBUF1[0]   | Encoder1 input buffer or Key1 input<br>buffer | 0x00           |

|                               | WR | [7:0]    |                                            | Encoder1 input buffer or Key1 input<br>buffer | 0x00           |

| 1031F                         |    | [7:0]    | RG_EEBUF[31]<br>MCU :<br>RG_ENCINBUF1[15]  | Encoder1 input buffer or Key1 input<br>buffer | 0x00           |

| 0x10320                       |    | [7:0]    | RG_EEBUF[32]<br>MCU :<br>RG_ENCOUTBUF0[0]  | Encoder0 output buffer                        | 0x00           |

|                               | WR | [7:0]    |                                            | Encoder0 output buffer                        | 0x00           |

| 1032F                         |    | [7:0]    | RG_EEBUF[47]<br>MCU :<br>RG_ENCOUTBUF0[15] | Encoder0 output buffer                        | 0x00           |

| 0x10330                       |    | [7:0]    | RG_EEBUF[48]<br>MCU :<br>RG_ENCOUTBUF1[0]  | Encoder1 output buffer                        | 0x00           |

|                               | WR | [7:0]    |                                            | Encoder1 output buffer                        | 0x00           |

| 1033F                         |    | [7:0]    | RG_EEBUF[63]<br>MCU :<br>RG_ENCOUTBUF1[15] | Encoder1 output buffer                        | 0x00           |

| RESERVED                      |    |          | RESERVED                                   |                                               |                |

| RG_EEBUF400<br>Use this regis |    | is the i | nput and output buffer wh                  | en performing AES decryption.                 |                |

| 0x10400                       | WR | [7:0]    | RG_EEBUF[0]<br>MCU : RG_DECINBUF0[0]       | Decoder0 input buffer or Key0 input<br>buffer | 0x00           |

| ADDR(HEX) | WR | BIT   | NAME/RANGE                                 | DESCRIPTION                                   | RESET<br>VALUE |  |       |                                            |                        |      |

|-----------|----|-------|--------------------------------------------|-----------------------------------------------|----------------|--|-------|--------------------------------------------|------------------------|------|

|           |    | [7:0] |                                            | Decoder0 input buffer or Key0 input<br>buffer | 0x00           |  |       |                                            |                        |      |

| 1040F     |    | [7:0] | RG_EEBUF[15]<br>MCU :<br>RG_DECINBUF0[15]  | Decoder0 input buffer or Key0 input<br>buffer | 0x00           |  |       |                                            |                        |      |

| 0x10410   |    | [7:0] | RG_EEBUF[16]<br>MCU : RG_DECINBUF1[0]      | Decoder1 input buffer or Key1 input<br>buffer | 0x00           |  |       |                                            |                        |      |

|           | WR | [7:0] |                                            | Decoder1 input buffer or Key1 input<br>buffer | 0x00           |  |       |                                            |                        |      |

| 1041F     |    | [7:0] | RG_EEBUF[31]<br>MCU :<br>RG_DECINBUF1[15]  | Decoder1 input buffer or Key1 input<br>buffer | 0x00           |  |       |                                            |                        |      |

| 0x10420   |    | [7:0] | RG_EEBUF[32]<br>MCU :<br>RG_DECOUTBUF0[0]  | Decoder0 output buffer                        | 0x00           |  |       |                                            |                        |      |

|           | WR | [7:0] |                                            | Decoder0 output buffer                        | 0x00           |  |       |                                            |                        |      |

| 1042F     |    |       |                                            |                                               |                |  | [7:0] | RG_EEBUF[47]<br>MCU :<br>RG_DECOUTBUF0[15] | Decoder0 output buffer | 0x00 |

| 0x10430   |    | [7:0] | RG_EEBUF[48]<br>MCU :<br>RG_DECOUTBUF1[0]  | Decoder1 output buffer                        | 0x00           |  |       |                                            |                        |      |

|           | WR | [7:0] |                                            | Decoder1 output buffer                        | 0x00           |  |       |                                            |                        |      |

| 1043F     |    | [7:0] | RG_EEBUF[63]<br>MCU :<br>RG_DECOUTBUF1[15] | Decoder1 output buffer                        | 0x00           |  |       |                                            |                        |      |

## 6.1.2 REGISTER ADDRESS MAP

| ADDR(HEX)    | WR                | BIT      | NAME/RANGE             | DESCRIPTION                                                                                                                                                                                  | RESET<br>VALUE |

|--------------|-------------------|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| RG_SOFT_RE   | SET               |          |                        |                                                                                                                                                                                              |                |

|              |                   | [7:2]    | RESERVED               |                                                                                                                                                                                              |                |

| 0x10600      | WR                | [1]      | RG_SWRESET_EE          | Reset EEPROM. Test register. To reset<br>EEPROM, write 1 then Write 0 to this<br>register bit.<br>0 : Normal<br>1 : RESET                                                                    | 0x0            |

|              | WR                | [0]      | RG_SWRESET             | Reset symcipher hardware parts. To<br>reset symchpher hardware parts, write<br>1 then write 0 to this register bit.<br>0 : Normal<br>1 : RESET                                               | 0x0            |

| 0x10601      | А                 | -        | RG_ACCESS              | Use this register to control DALPU-3.<br>This register is access register. That is,<br>it is not a register that writes and<br>reads values.                                                 | -              |

| 0x10602      | А                 | _        | RG_ACCESS2             | Use this register to control DALPU-3.<br>This register is access register. That is,<br>it is not a register that writes and<br>reads values.<br>Used to control ST0_EEP_OW_CTRL<br>function. | -              |

| 0x10603      |                   |          | RESERVED               |                                                                                                                                                                                              |                |

| action on ea | ster to<br>ch fun | ction st | ate, go to ST0_STANDBY | ontrol state. When you finish the control<br>State and wait for the next control. The<br>function are shown below.                                                                           |                |

ST0\_STANDBY is in standby mode and in standby mode. The other state is the state that DALPU-3 performs specific actions. When DALPU-3 ends a particular operation, E-MCU sets this register to ST0\_STANDBY state.

| ADDR(HEX) | WR | BIT   | NAME/RANGE | DESCRIPTION | RESET<br>VALUE |

|-----------|----|-------|------------|-------------|----------------|

| 0x10604   |    | [7:4] | RESERVED   |             |                |

| To enter the desired main state, write<br>the following corresponding values in<br>this register : To end control and<br>change to standby state, write a value<br>of " 0x1 " to this reigister and write<br>access to the RG_ACCESS register.<br>4'h1 : Set main state(ST0) to<br>ST0_STANDBY state.<br>4'h5 : Set main state(ST0) to ST0_CM0<br>state.<br>4'h6 : Set main state(ST0) to ST0_CM0<br>state.<br>4'h7 : Set main state(ST0) to<br>ST0_STDSPI state.<br>4'h7 : Set main state(ST0) to<br>ST0_EE_CFG state.<br>4'h8 : Set main state(ST0) to<br>ST0_RANDOM state.<br>4'h9 : Set main state(ST0) to<br>ST0_SYMCIP state.<br>4'hA : Set main state(ST0) to ST0_OKA<br>state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADDR(HEX) | WR      | BIT   | NAME/RANGE       | DESCRIPTION                            | RESET<br>VALUE |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|------------------|----------------------------------------|----------------|

| WR       [3:0]       RG_ST0_OPMODE       the following corresponding values in this register : To end control and change to standby state, write a value of "0x1 " to this reigister and write access to the RG_ACCESS register.         WR       [3:0]       RG_ST0_OPMODE       ST0_STANDBY state.         WR       [3:0]       RG_ST0_OPMODE       ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |         |       |                  | To enter the desired main state, write | VALUE          |

| WR       [3:0]       RG_ST0_OPMODE         WR       [3:0]       RG_ST0_OPMODE         Image to standby state.       4'h1 : Set main state(ST0) to ST0_CM0 state.         4'h7 : Set main state(ST0) to ST0_CM0 state.       4'h7 : Set main state(ST0) to ST0_CM0 state.         4'h7 : Set main state(ST0) to ST0_CM0 state.       4'h7 : Set main state(ST0) to ST0_CM0 state.         4'h7 : Set main state(ST0) to ST0_CM0 state.       4'h7 : Set main state(ST0) to ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEchange to standby state, write a value<br>of " 0x1 " to this reigister and write<br>access to the RG_ACCESS register.<br>4'h1 : Set main state(ST0) to<br>ST0_STANDBY state.<br>4'h5 : Set main state(ST0) to ST0_CMO<br>state.<br>4'h6 : Set main state(ST0) to ST0_CMO<br>state.<br>4'h7 : Set main state(ST0) to<br>ST0_ETCFG state.<br>4'h8 : Set main state(ST0) to<br>ST0_ST0_ETCFG state.<br>4'h8 : Set main state(ST0) to<br>ST0_ST0_DTG<br>ST0_ST0_ETCFG state.WR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0)RG_ST0_CPMODEWR(3:0) <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                        |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEG_ST0_STANDBY state.4'h5 : Set main state(ST0) to ST0_CM0 state.4'h7 : Set main state(ST0) to ST0_CM0 state.4'h6 : Set main state(ST0) to ST0_CM0 state.4'h7 : Set main state(ST0) to ST0_CTSPI state.4'h7 : Set main state(ST0) to ST0_ST0_SF0 state.4'h7 : Set main state(ST0) to ST0_ST0_FCFG state.4'h7 : Set main state(ST0) to ST0_STMCIP state.4'h8 : Set main state(ST0) to ST0_OFMODEST0_STMCIP state.4'h7 : Set main state(ST0) to ST0_OFMODEST0_MIDR state.4'h7 : Set main state(ST0) to ST0_OFMODEST0_STMCIP state.4'h7 : Set main state(ST0) to ST0_OFMODEST0_MIDR state.4'h7 : Set main state(ST0) to ST0_OFMODEST0_ST0_MIDR state.4'h7 : Set main state(ST0) to ST0_OFMODEST0_ST0_OFMODE5T0_STANDBY -> ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEA'hF : Set main state(ST0) to<br>ST0_ST0_ST0.ST0.ST0.ST0.ST0.ST0.ST0.ST0.ST0.ST0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |         |       |                  |                                        |                |

| <ul> <li>WR [3:0]</li> <li>RG_ST0_OPMODE</li> <li>WR [3:0]</li> <li>RG_ST0_OPMODE</li> <li>WR [3:0]</li> <li>KG_ST0_OPMODE</li> <li>A'h7 : Set main state(ST0) to ST0_CMA state.</li> <li>4'h7 : Set main state(ST0) to ST0_CKA state.</li> <li>4'h8 : Set main state(ST0) to ST0_OKA state.</li> <li>4'h9 : Set main state(ST0) to ST0_OKA state.</li> <li>4'h7 : Set main state(ST0) to ST0_OKA state.</li> <li>4'h8 : Set main state(ST0) to ST0_OKA state.</li> <li>4'h7 : Set main state(ST0) to ST0_CEP_OW_CTRL state.</li> <li>4'h7 : Set main state(ST0) to ST0_EP_CM_CTRL state.</li> <li>5T0_STANDBY -&gt; ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_</li></ul>                                                                                                                                                                                                                                             |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEWR[3:0]RG_ST0_OPMODEKG_ST0_ST0_CRANDORState.KG_ST0_OPMODEST0_EE_CFG state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_ST0_SYMCIP state.KG_ST0_OPMODEST0_ST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_SYMCIP state.KG_ST0_OPMODEST0_ST0_SYMCIP state.KG_ST0_OPMODEST0_ST0_SYMCIP state.KG_ST0_OPMODEST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |         |       |                  |                                        |                |

| WR       [3:0]       RG_ST0_OPMODE       4'h5 : Set main state(ST0) to ST0_CM0 state.         WR       [3:0]       RG_ST0_OPMODE       State.         Yh5 : Set main state(ST0) to ST0_CKA state.       4'h7 : Set main state(ST0) to ST0_CKA state.         Yh6 : Set main state(ST0) to ST0_OKA state.       4'h8 : Set main state(ST0) to ST0_OKA state.         Yh7 : Set main state(ST0) to ST0_OKA state.       4'h8 : Set main state(ST0) to ST0_OKA state.         Yh7 : Set main state(ST0) to ST0_OKA state.       4'h8 : Set main state(ST0) to ST0_OKA state.         Yh7 : Set main state(ST0) to ST0_OKA state.       4'h8 : Set main state(ST0) to ST0_OKA state.         Yh7 : Set main state(ST0) to ST0_OKA state.       4'h7 : Set main state(ST0) to ST0_OKA state.         Yh7 : Set main state(ST0) to ST0_OKA state.       4'h7 : Set main state(ST0) to ST0_PERM_GET state.         Yh7 : Set main state(ST0) to ST0_PERM_GET state.       4'h7 : Set main state(ST0) to ST0_PERM_GET state.         Yh8 : Set main state(ST0) to ST0_CTRL state.       The correct order of control for this register is as follows.         (Correct use examples.)       PWR_ON(or SW RESETB)-> ST0_STANDBY -> ST0_STANDBY -> ST0_STANDBY -> ST0_STANDBY -> ST0_CM0 -> ST0_STANDBY -> ST0_ST |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEstate.4'h6 : Set main state(ST0) to<br>ST0_STDSPI state.4'h7 : Set main state(ST0) to<br>ST0_EE_CFG state.WR[3:0]RG_ST0_OPMODEST0_SYMCIP state.(3:0)RG_ST0_OPMODEstate.4'h7 : Set main state(ST0) to<br>ST0_SYMCIP state.4'h6 : Set main state(ST0) to<br>ST0_SYMCIP state.WR[3:0]RG_ST0_OPMODEWR(3:0)RG_ST0_OPMODEWR(3:0)RG_ST0_OPMODEWR(3:0)RG_ST0_OPMODEWR(3:0)ST0_ST0_CTRL state.4'h7 : Set main state(ST0) to<br>ST0_PERM_GET state.4'h7 : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.HH6 : Set main state(ST0) to<br>ST0_STANDBY -> ST0_STDSPI-><br>ST0_STANDBY -> ST0_STDSPI-><br>ST0_STANDBY -> ST0_CM0 -><br>ST0_STANDBY -> ST0_EE_CFG -><br>ST0_STANDBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |         |       |                  |                                        |                |

| WR       [3:0]       RG_ST0_OPMODE       4'h6 : Set main state(ST0) to         ST0_ST0_SPI state.       4'h7 : Set main state(ST0) to         ST0_EE_CFG state.       4'h8 : Set main state(ST0) to         ST0_RANDOM state.       4'h9 : Set main state(ST0) to         ST0_SYMCIP state.       4'h4 : Set main state(ST0) to         ST0_SYMCIP state.       4'h4 : Set main state(ST0) to ST0_OKA         state.       4'h8 : Set main state(ST0) to ST0_OKA         ST0_MIDR state.       4'h7 : Set main state(ST0) to         4'h7 : Set main state(ST0) to       ST0_PERM_GET state.         4'h7 : Set main state(ST0) to       ST0_EEP_OW_CTRL state.         The correct order of control for this       register is as follows.         (Correct use examples.)       PWR_ON(or SW RESETB)->         ST0_STANDBY -> ST0_STDSPI->       ST0_STANDBY -> ST0_EE_CFG ->         ST0_STANDBY       ST0_EE_CFG ->                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |         |       |                  |                                        |                |

| WR       [3:0]       RG_ST0_OPMODE       4'h7 : Set main state(ST0) to<br>ST0_EE_CFG state.         WR       [3:0]       RG_ST0_OPMODE       6'h8 : Set main state(ST0) to<br>ST0_SYMCIP state.         WR       [3:0]       RG_ST0_OPMODE       6'h8 : Set main state(ST0) to<br>ST0_SYMCIP state.         WR       [3:0]       RG_ST0_OPMODE       6'h8 : Set main state(ST0) to<br>ST0_SYMCIP state.         WR       [3:0]       RG_ST0_OPMODE       6'h8 : Set main state(ST0) to<br>ST0_ST0_MIDR state.         4'h7 : Set main state(ST0) to<br>ST0_PERM_GET state.       6'h8 : Set main state(ST0) to<br>ST0_PERM_GET state.         4'h7 : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.       6'h7 : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.         WR       NR       1'h7 : ST0_STANDBY -> ST0_ST0SPI-><br>ST0_STANDBY -> ST0_ST0_ST0SPI-><br>ST0_STANDBY -> ST0_CM0 -><br>ST0_STANDBY -> ST0_EE_CFG -><br>ST0_STANDBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEST0_EE_CFG state.4'h8 : Set main state(ST0) to<br>ST0_RANDOM state.4'h9 : Set main state(ST0) to<br>ST0_SYMCIP state.WR[3:0]RG_ST0_OPMODE4'h2 : Set main state(ST0) to ST0_OKA<br>state.WR[3:0]RG_ST0_OPMODEStop<br>Ather is set main state(ST0) to ST0_OKA<br>state.WR[3:0]RG_ST0_OPMODE4'h2 : Set main state(ST0) to ST0_OKA<br>ST0_MIDR state.WR[3:0]RG_ST0_OPMODEStop<br>Ather is set main state(ST0) to ST0_OKA<br>ST0_MIDR state.WR[3:0]RG_ST0_OPMODEA'h6 : Set main state(ST0) to<br>ST0_MIDR state.WR(Stop<br>CT0_ST0_EEP_OW_CTRL state.A'h7 : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.WR(Correct use examples.)PWR_ON(or SW RESETB)-><br>ST0_STANDBY -> ST0_ST0_STDSPI-><br>ST0_STANDBY -> ST0_ST0_CM0 -><br>ST0_STANDBY -> ST0_EC_CFG -><br>ST0_STANDBY -> ST0_EC_CFG -><br>ST0_STANDBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODE4'h8 : Set main state(ST0) to<br>ST0_RANDOM state.<br>4'h9 : Set main state(ST0) to ST0_OKA<br>state.<br>4'hA : Set main state(ST0) to ST0_OKA<br>state.<br>4'hB : Set main state(ST0) to<br>ST0_MIDR state.<br>4'hC : Set main state(ST0) to<br>ST0_PERM_GET state.4'hF : Set main state(ST0) to<br>ST0_PERM_GET state.''hC : Set main state(ST0) to<br>ST0_PERM_GET state.4'hF : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.<br>The correct order of control for this<br>register is as follows.<br>(Correct use examples.)<br>PWR_ON(or SW RESETB)-><br>ST0_STANDBY -> ST0_STDSPI-><br>ST0_STANDBY -> ST0_EE_CFG -><br>ST0_STANDBY -> ST0_EE_CFG ->                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEST0_RANDOM state.WR[3:0]RG_ST0_OPMODEST0_SYMCIP state.4'hA : Set main state(ST0) to ST0_OKA<br>state.state.4'hB : Set main state(ST0) to<br>ST0_MIDR state.'hA : Set main state(ST0) to<br>ST0_MIDR state.4'hC : Set main state(ST0) to<br>ST0_PERM_GET state.'hA : Set main state(ST0) to<br>ST0_PERM_GET state.4'hF : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.'hA : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.4'hF : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.'hA : Set main state(ST0) to<br>ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |         |       |                  |                                        |                |

| WR [3:0] RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_OPMODE<br>RG_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0_ST0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |         |       |                  |                                        |                |

| WR[3:0]RG_ST0_OPMODEST0_SYMCIP state.<br>4'hA : Set main state(ST0) to ST0_OKA<br>state.<br>4'hB : Set main state(ST0) to<br>ST0_MIDR state.<br>4'hC : Set main state(ST0) to<br>ST0_PERM_GET state.4'hF : Set main state(ST0) to<br>ST0_PERM_GET state.A'hF : Set main state(ST0) to<br>ST0_EEP_OW_CTRL state.<br>The correct order of control for this<br>register is as follows.<br>(Correct use examples.)<br>PWR_ON(or SW RESETB)-><br>ST0_STANDBY -> ST0_STDSPI-><br>ST0_STANDBY -> ST0_EE_CFG -><br>ST0_STANDBY -> ST0_EE_CFG -><br>ST0_STANDBY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |         |       |                  |                                        |                |